RF入力とSTD入力の感度は下のグラフのようになっています。

10MHz基準信号入力は約-20dBm、100MHz台のRF信号入力は約-40dBmから動作します。

逆に、入力レベルの上限は、ICへの過大入力レベルを「電源電圧の範囲を超えるレベル」と考えると、約13dBmとなります。

使用にあたっては、基準信号の入力レベルが大きくなりすぎないように注意してください。

Solilock Ver.3

Solilock Ver.3は、分周器と位相比較器にPLL ICを使い、分周比などの設定用のマイコン(MSP430F1121A)を搭載しました。分周比などのデータはマイコン内蔵のフラッシュメモリに記憶しています。このフラッシュメモリのデータはパソコンから書き換え可能ですので、ユーザーが自由にPLLの設定を変更出来ます。

パソコンからのデータ書き換えツール「Solilock Configurator」も公開しています。

Solilock3は開発以来100枚以上製作しました。ユーザーの皆さんが、国内最大ユーザー数を誇る(と思う)M電機のUTVシリーズ、世界で有名なDB6NT基板にインプリし、トランスバータの安定化を実現されています。現在では各社製品ともPLLによる外部同期が標準装備となっています。

現在でも自作局発の安定化のお役に立っているようです。

さらに

Solilock G は、7GHzまで動作するように回路を変更したものです。

UTV-10Gへの組込例 7L1RLL Rickの実験です。

Amateur Radio Activities by RLL(RLLのアマチュア無線活動)

のページ中

Installation of PLL in a 10GHz

Transverter(10GHzトランスバータのPLL化,XMLfile)

信号の入力レベルについて

RF入力とSTD入力の感度は下のグラフのようになっています。

10MHz基準信号入力は約-20dBm、100MHz台のRF信号入力は約-40dBmから動作します。

逆に、入力レベルの上限は、ICへの過大入力レベルを「電源電圧の範囲を超えるレベル」と考えると、約13dBmとなります。

使用にあたっては、基準信号の入力レベルが大きくなりすぎないように注意してください。

Solilock Ver.3の開発

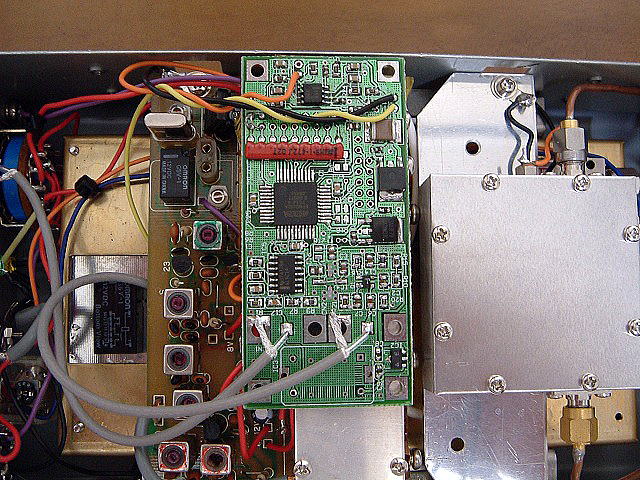

↓UTV-24Gで実験中の様子

主な変更点

| 項目 | 内容 |

| 低消費電力化 |

・地球に優しい。 |

| ロック検出信号 |

・ロック時にLEDが点灯します。 |

| パソコンからの周波数設定機能追加 | ・PLLの分周比、ループゲイン、極性などをパソコンから変更できます。パソコンソフトは配布。RS232Cのレベルコンバータは別途用意してください |

| 大出力振幅化 |

VCXO制御電圧出力範囲が0〜8V以上まで広くなりました。(D1:HZM10を外すと、ほぼ電源電圧まで上昇します。) |

| 業者による半田付け | 半田付けがきれいになります。 |

回路の説明

VCO入力部(RF入力)

VCXO入力は回路に与える影響をするなくするためFETで受けていますが、影響がゼロではないので注意して下さい。

・直列に抵抗、小容量のコンデンサを挿入して信号を取り出す。

・同調回路の再調整。

などの検討が必要になる可能性があります。UTV−24Gに取り付けた場合は、逓倍回路の同調回路の再調整が必要でした。

FETアンプの周波数特性から、入力感度は100MHz程度から徐々に悪くなります。100MHzでは−10dBm(50Ω時)で動作します。ICのスペックでは165MHzまで制御可能です。

基準信号入力部

基準信号は100MHzまでOKです。

信号源のインピーダンスが50Ωのときは入力を50Ωで終端してください。

信号レベルは−5dBm(50Ω時)以上にしてください。

なお、基板上に発振モジュールを乗せられるようにパターンを書いてあります。

位相比較器

PLLIC内蔵の位相比較器は、位相比較周波数を最高55MHzまで設定可能です。

ループフィルタ

位相誤差出力はループフィルタを通してVCXOの制御電圧になります。CN3の出力をVCXOのバリキャップに接続してください。VCXOは制御電圧が上がると周波数が上がるようにしてください。

ループフィルタは以下の条件で設計したものを実装しています。

・VCXO感度:100Hz/1V

・位相比較周波数:100KHz

・ループ帯域:約50Hz

R7、R8、R31、C14、C23がループフィルタの特性を決定しています。

2段目のオペアンプは位相比較周波数のスプリアスを抑制するものです。同時に約2倍のDC増幅をしています。

ループフィルタの定数を検討するときは以下のURLでダウンロードできる「ADIsimPLL」を利用してみてください。

http://www.analog.com/

CPU関連

TIの超ローパワーCPU(MSP430F1121A)を使ってPLL ICのレジスタ設定(分周比などの設定)を行っています。

電源投入直後にレジスタの設定を行った後にクロックを停止して完全に動作をとめるのでCPUが原因のノイズの発生はゼロです。

レジスタの設定値はCPU内蔵のフラッシュメモリに記憶してあります。フラッシュメモリの内容は、専用プログラム(slconfig.exe)を使ってシリアルI/Fから書き換え可能です。

JP1は分周比の切替用のジャンパです。後述の「使い方」を参照して下さい。

CN5はシリアルI/Fです。後述するプログラムを使って貴兄オリジナルのレジスタ設定にする場合は、0−3Vの信号をRS232Cレベルに変換する回路(Sipex3232などのIC)を使ったレベルコンバーターを介してPCに接続してください。

ロック表示

J3の1−2pinにLEDを取り付けてください。1pinがアノード、2pinがカソードです。

PLLがロックしたときに点灯します。

UTV−24Gに取り付けた様子

周波数の設定

Solilock3にはあらかじめ8パターンの周波数が設定されています。設定はJP1−1〜JP1−3で切り替えます。

ver3.1の周波数設定

| ターゲットの周波数(MHz) | 応用例 | JP1-1 | JP1-2 | JP1-3 |

| 100 | open | open | open | |

| 111.8 | UTV-10G | short | open | open |

| 113.7 | UTV-24G | open | short | open |

| 114.55 | UTV-47G | short | short | open |

| 118.333 | UTV-5.6G(IF=430MHz) | open | open | short |

| 112 | UTV-5.6G(IF=1200MHz) | short | open | short |

| 119.2708 | 11.45GHz | open | short | short |

| 122.9167 | 11.8GHz | short | short | short |

| ターゲットの周波数(MHz) | 応用例 | JP1-1 | JP1-2 | JP1-3 |

| 100 | open | open | open | |

| 111.8 | UTV-10G | short | open | open |

| 113.7 | UTV-24G(IF=1280MHz) | open | short | open |

| 114.55 | UTV-47G | short | short | open |

| 118.333 | UTV-5.6G(IF=430MHz) | open | open | short |

| 112 | UTV-5.6G(IF=1200MHz) | short | open | short |

| 113.75 | UTV-24G(IF=1270MHz) | open | short | short |

| 122.9167 | 11.8GHz | short | short | short |

Solilock Ver.1

バージョン1は、CT1DMKのreflockと同様に、分周器、位相比較器にCPLDを使用したものです。

入力アンプの微妙な定数、CPLDの内部回路などはreflockとは別の物なので「Solilock」と命名しました。しかし、今考えるとオリジナルほとんど同じとみなしてもいいでしょう。

CPLD

reflockでは、分周比が日本国内No1実績のUTVシリーズに合わないため、新たなプログラムを製作者に依頼する必要があり、これがJAでの普及の妨げになっていたようです。

そこで、reflockとピン配置に互換を持たせたJA向けのCPLDを開発しました。

併せて、不安定な入力アンプを手直ししました。

CPLDのソースコード、pofファイルはこちら

取説、回路図はこちら

CT1DMKが発表したreflockをJA国内で多く使われているトランスバータに対応させた応用型です。

愛称としてSolilockと呼んでいます。

バージョン1は、CT1DMKのreflockと同様に、分周器、位相比較器にCPLDを使用したものです。

入力アンプの微妙な定数、CPLDの内部回路などはreflockとは別の物なので「Solilock」と命名しました。しかし、今考えるとオリジナルほとんど同じとみなしてもいいでしょう。

CPLD

reflockでは、分周比が日本国内No1実績のUTVシリーズに合わないため、新たなプログラムを製作者に依頼する必要があり、これがJAでの普及の妨げになっていたようです。

そこで、reflockとピン配置に互換を持たせたJA向けのCPLDを開発しました。

併せて、不安定な入力アンプを手直ししました。

CPLDのソースコード、pofファイルはこちら

取説、回路図はこちら

製作したSolilockをマキ電機のUTV-24Gに組み込んで見ました。

組み込み方法はこちら。

問題点

実際に組み込んでみると幾つかの問題点が有りました。

| 1 | 基準信号(10MHz)のレベルが低いとジッターが増えることがある。 | 2Vp−pくらいつっこむと良い。→必要なら外部でアンプする。 |

| 2 | UTVの局発回路は意外と短期間の変動が大きい。 (外乱に弱い) |

solilockの帯域を広くする→フィルタ定数の変更 |

| 3 | UTVのフタをあけたままでは、局発がふらふらする。(2と同じ) | 未解決。フタをするしかない。(実験がめんどくさい) |

| 4 | solilockから出るスプリアスがUTVのIF信号(1200MHz)に飛び込むコトがある。 | 未解決 |

| 5 | 制御電圧の振幅が狭い | ・VXCOの温度特性を補償する。 ・VXCOの可変幅を変更する。 ・OPAMP回路の修正。 |

| 6 | ロックデテクタが欲しい |

以上の問題点を踏まえ、回路の全面見直しをする事にしました。