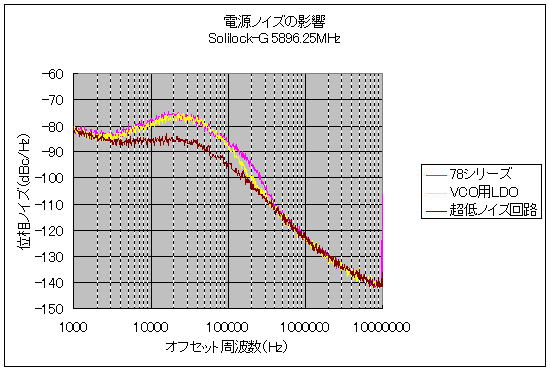

埵憡僲僀僘偵偮偄偰

埵憡僲僀僘偼丄怣崋偵嶨壒偑崿偞偭偰埵憡傪僈僠儍僈僠儍偲曄摦偝偣傞僲僀僘偺偙偲偱偡丅

敪惗尨場偼丄夞楬傪峔惉偡傞慺巕偑敪惗偡傞彅乆偺嶨壒偱偡丅

Solilock-G偺幚尡偱偼丄埵憡僲僀僘偺應掕偵僕儍儞應偱埨壙偵弌夞偭偰偄傞亂hp亃偺4352B亄43521A亄8665B傪巊梡偟偰偄傑偡丅

丒應掕宯偺應掕尷奅乮巆棷僲僀僘乯偼丠

丒婎弨怣崋偺塭嬁偼丠

丒VCO揹尮夞楬偺僲僀僘偺塭嬁偼丠

應掕宯偺應掕尷奅

4352B偺應掕尷奅偼丄應掕偵巊偆SSG乮偙偙偱偼8665B乯偺埵憡僲僀僘偵埶懚偟傑偡丅

偦偙偱丄8665B偲傎傏摨偠埵憡僲僀僘偱偼側偄偐偲巚偆8664A偺怣崋偺埵憡僲僀僘傪應掕偟偰丄應掕尷奅傪悇應偟傑偡丅

斾妑偺偨傔丄UNITEC-1庴怣宯偺専摙偵偮偐偭偨Solilock-G乮5840MHz丄埵憡斾妑10MHz乯偺應掕寢壥傪崌傢偣偰昞帵偟傑偡丅

8664A偐傜偼2920MHz傪弌椡偟丄2掽攞婍偱5840MHz偵偟偰偄傑偡丅

應掕寢壥偼壓偺僌儔僼偺捠傝偱偡丅

應掕宯偺僨乕僞偼丄-6dB偝偘偰昞帵偟偰偁傝傑偡丅尩枾偵偼6dB偱偼側偄偲巚偄傑偡偑丄偞偭偔傝恑傔傑偟偨丅

(偙傟娫堘偭偰偄傑偡偹丅摨偠廃攇悢偩偲偟偰-3dB偱偡偹)

偙偺僨乕僞偐傜丄-90dBc偲偐-100dBc傪媍榑偡傞偲偒偵偼丄4352B偱偼悢kHz埲壓偺僨乕僞偼巊偊側偄偲偄偆偙偲偑尵偊傑偡丅

傕偭偲椙偄應掕婍偑梸偟偔側偭偪傖偄傑偡偹丅

婎弨怣崋偺塭嬁

Solilock-G乮偵尷傜偢PLL敪怳婍偼乯偼丄GHz懷VCO偺怣崋傪婎弨怣崋偺埵憡偵摨婜偝偣傞摦嶌傪偟偰偄傑偡丅

婎弨偲側傞怣崋偵埵憡僲僀僘偑偁傞偲丄VCO偺弌椡怣崋偵傕埵憡僲僀僘偑僐僺乕偝傟偰偟傑偄傑偡丅

偝傜偵丄偨偲偊偽10MHz偺婎弨怣崋傪巊偭偰5000MHz偺VCO偵PLL傪偐偗傞偲丄婎弨怣崋偺埵憡僲僀僘偼50dB乮20log乮5000MHz/10MHz乯乯嫮挷偝傟偰5000MHz偺怣崋偵尰傟傑偡丅

廬偭偰丄僗儁傾僫摍偱偼尒偊側偄10MHz偺埵憡僲僀僘偑5000MHz偱偼僴僢僉儕偲尒偊偰偟傑偄傑偡丅

Solilock-G偺婎弨怣崋擖椡偵丄偄偔偮偐偺10MHz怣崋尮傪愙懕偟偰傒偰弌椡偺埵憡僲僀僘偵偳偺傛偆側嵎偑桳傞偺偐傪尒偰傒傑偟偨丅

傑偨丄應掕婍偵撪憼偝傟偰偄傞偙偲偑懡偄TCO627B偼丄SC僇僢僩偺VCXO偵斾傋偰栺10dB偔傜偄嶨壒儗儀儖偑崅偄傛偆偱偡丅

VCO揹尮夞楬偺僲僀僘偺塭嬁

VCO偺敪怳廃攇悢偼揹尮揹埑偵傛偭偰傕曄摦偟傑偡丅

VCO偺揹尮偵嶨壒偑忔偭偰偄傞偲敪怳弌椡偺埵憡僲僀僘偑憹壛偟傑偡丅

VCO偺揹尮夞楬傪曄偊傞偲埵憡僲僀僘偵偳偺傛偆側曄壔偑偁傞偐傪幚尡偟偰傒傑偟偨丅

幚尡悈弨

乮侾乯俈俉僔儕乕僘偺嶰抂巕儗僊儏儗乕僞丅弌椡-GND娫偵330uF傪愙懕偟偰偄傑偡丅

乮俀乯VCO梡揹尮偲偟偰敪攧偝傟偰偄傞儗僊儏儗乕僞丅僗儁僢僋偱偼僲僀僘揹埑=40uV偲側偭偰偄傑偡丅

乮俁乯SolilockG偱嵟廔揑偵扝傝拝偄偨挻掅嶨壒揹尮夞楬丅

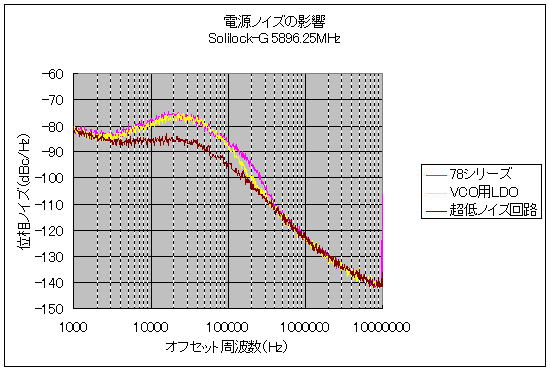

5896.25MHz偺Solilock-G偺VCO揹尮夞楬傪乮侾乯丄乮俀乯丄乮俁乯偺3悈弨偱摦嶌偝偣丄埵憡僲僀僘偺堘偄傪斾傋偰傒傑偟偨丅

10kHz乣200kHz偱埵憡嶨壒偺儗儀儖偵嵟戝10dB傕嵎偑偁傝傑偡丅78僔儕乕僘亄330uF偲掅僲僀僘LDO偱偼戝嵎偑柍偄偺傕暘偐傝傑偡丅